低温存内计算是实现数据密集型高能效计算的一项技术方案。针对现有存内计算设计在低温器件特性利用上的不足,金沙集团1862cc信息科学与技术学院哈亚军课题组提出了一种基于eDRAM的低温存内计算加速器(eCIMC),可支持布尔计算和卷积计算操作。

图1 eCIMC整体架构以及核心C3T块设计

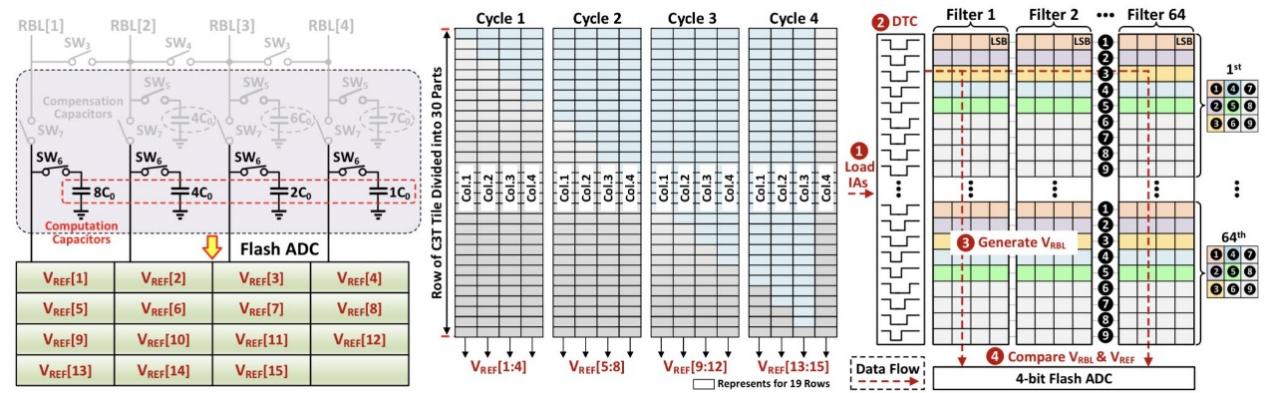

图2 基于ARSA的4-bit Flash ADC结构以及多周期参考电压自适应生成技术示意图

本研究通过优化C3T动态存储单元结构,成功实现了支持高保持时间的多模式操作;设计了一种自适应可重构的灵敏放大器(ARSA),充分利用C3T结构特性实现参考电压存储,显著提升了计算能效。在此基础上,团队通过重构ARSA实现4-bit Flash ADC,并结合多周期的参考电压自适应生成技术,实现了快速且低功耗的低温卷积计算。在这个过程中,信息科学与技术学院寇煦丰课题组所提出的低温器件模型对本工作电路设计与优化起到重要作用。

该成果以题为“eCIMC: A 603.1TOPS/W eDRAM-based Cryogenic In-Memory Computing Accelerator Supporting Boolean/Convolutional Operations”被集成电路领域国际知名期刊IEEE Journal of Solid-State Circuits(简称JSSC)接收。信息学院2021级博士研究生束宇豪为本工作第一作者、信息学院2023届博士生张宏图为第二作者,哈亚军教授为通讯作者,这是我校首次以第一作者单位在JSSC上发表论文。

沪公网安备 31011502006855号

沪公网安备 31011502006855号